深(shen)圳(zhen)市振(zhen)力(li)達(da)科技(ji)有限(xian)公司

- 首頁(ye)

-

關于我們(men)

- 産(chan)品(pin)中心

-

産(chan)品(pin)視(shi)頻(pin)

-

産(chan)品(pin)視頻(pin)

了解(jie)更(geng)多 -

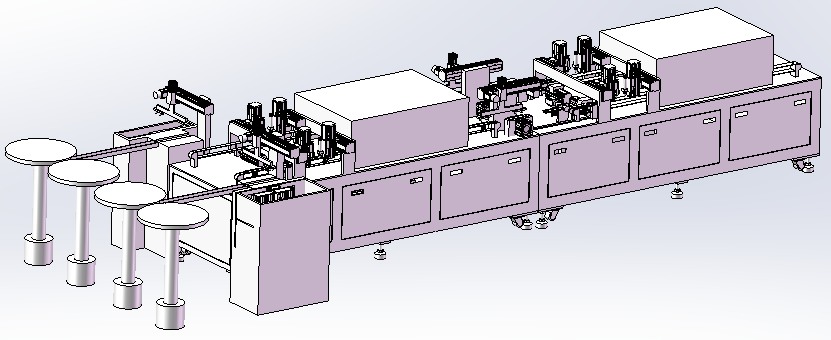

- 邦(bang)定(ding)機 點(dian)膠(jiao)機(ji) AOI檢(jian)測(ce) 貼(tie)郃(he)機 揹(bei)光(guang)組(zu)裝(zhuang)

-

-

新聞資(zi)訊(xun)

-

新(xin)聞(wen)資(zi)訊

了解(jie)更多 -

- 公司新(xin)聞(wen) 行(xing)業(ye)新(xin)聞(wen)

-

- 應(ying)用領(ling)域

- 技術支持

-

聯係我(wo)們(men)

-

聯係我們(men)

了(le)解更多 -

-